- 您现在的位置:买卖IC网 > Sheet目录1999 > ICS950218AF (IDT, Integrated Device Technology Inc)IC TIMING CTRL HUB P4 48-SSOP

2

Integrated

Circuit

Systems, Inc.

ICS950218

0466B—03/17/04

The ICS950218 is a single chip clock solution for desktop designs using the Intel Brookdale chipset with PC133 or DDR

memory. It provides all necessary clock signals for such a system.

The ICS950218 is part of a whole new line of ICS clock generators and buffers called TCH (Timing Control Hub). ICS is the

first to introduce a whole product line which offers full programmability and flexibility on a single clock device. This part

incorporates ICS's newest clock technology which offers more robust features and functionality. Employing the use of a

serially programmable I

2C interface, this device can adjust the output clocks by configuring the frequency setting, the output

divider ratios, selecting the ideal spread percentage, the output skew, the output strength, and enabling/disabling each

individual output clock. TCH also incorporates ICS's Watchdog Timer technology and a reset feature to provide a safe setting

under unstable system conditions. M/N control can configure output frequency with resolution up to 0.1MHz increment. With

all these programmable features ICS's, TCH makes mother board testing, tuning and improvement very simple.

General Description

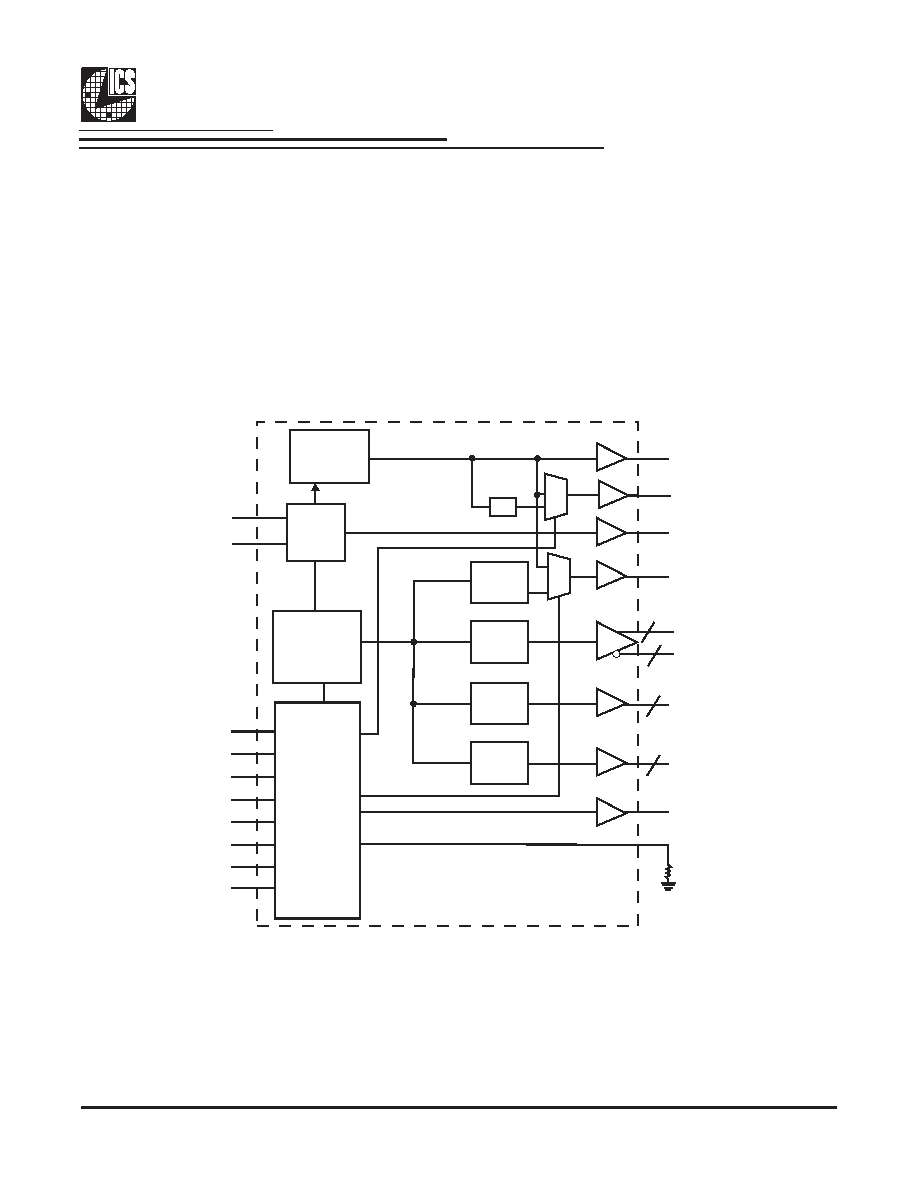

Block Diagram

PLL2

PLL1

Spread

Spectrum

48MHz

PCICLK (9:0)

3V66 (2:0)

24_48MHz

X1

X2

XTAL

OSC

CPU

DIVDER

PCI

DIVDER

3V66

DIVDER

PD#

MULTSEL(1:0)

SDATA

SCLK

Vtt_PWRGD#

SEL 48_24#

SEL 66_48#

FS (4:0)

I REF

RESET#

Control

Logic

Config.

Reg.

REF (1:0)

3

10

4

3

CPUCLKT (2:0)

CPUCLKC (2:0)

/ 2

3V66

DIVDER

3V66_48MHz

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS950908BFLF

IC TIMING CTRL HUB P4 56-SSOP

ICS951402AGLF

IC TIMING CTRL HUB P4 48-TSSOP

ICS95V847AGIT

IC CLOCK DRIVER 2.5V 24-TSSOP

ICS95V850AGT

IC CLK DVR PLL 1:10 48TSSOP

ICS95V857ALT

IC CLK DVR PLL 1:10 40TVSOP

ICS95V857CKLF8

IC CLK DVR PLL 1:10 40VFQFN

ICS97U870AKT

IC CLK DVR PLL 1:10 40VFQFN

ICS97ULP877AHT

IC CLOCK DRIVER 1.8V LP 52-BGA

相关代理商/技术参数

ICS950218AFLF

功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS950218AFLFT

功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS950218AFT

功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS950218YFLF-T

制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub TM for P4 TM

ICS950220

制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub⑩ for P4⑩

ICS950220AFLF

功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS950220AFLFT

功能描述:IC TIMING CTRL HUB P4 48-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:TCH™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS950220YFLFT

制造商:ICS 制造商全称:ICS 功能描述:Programmable Timing Control Hub⑩ for P4⑩